Difference between revisions of "RK3399"

Jump to navigation

Jump to search

| Line 2: | Line 2: | ||

== Specification == | == Specification == | ||

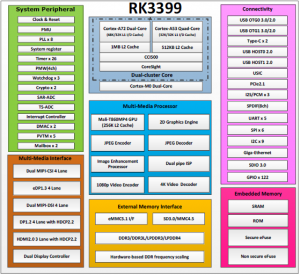

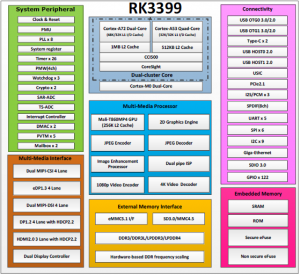

| + | [[File:RK3399 Block Diagram.png|thumb|right|RK3399 block diagram. Source: [http://opensource.rock-chips.com/images/5/5a/RK3399_Block_Diagram.png]]] | ||

*CPU: | *CPU: | ||

| − | **Big.Little architecture: Dual Cortex-A72 + Quad Cortex-A53, 64-bit CPU | + | **[[Big.Little architecture]]: Dual [[Cortex-A72]] + Quad [[Cortex-A53]], 64-bit CPU |

**Frequency is over 1.8GHz (Big cluster) | **Frequency is over 1.8GHz (Big cluster) | ||

**L1 cache | **L1 cache | ||

| Line 15: | Line 16: | ||

**4KB used by bootrom when bootup | **4KB used by bootrom when bootup | ||

*GPU: | *GPU: | ||

| − | ** Mali-T864 GPU, OpenGL ES1.1/2.0/3.0/3.1, OpenCL, DX11 | + | ** [[Mali-T864]] GPU, OpenGL ES1.1/2.0/3.0/3.1, OpenCL, DX11 |

**Supports AFBC (ARM Frame Buffer Compression) | **Supports AFBC (ARM Frame Buffer Compression) | ||

*Display: | *Display: | ||

Latest revision as of 21:12, 24 March 2020

Rockchip ARM processor found on e.g. Orange Pi 4.

Specification

RK3399 block diagram. Source: [1]

- CPU:

- Big.Little architecture: Dual Cortex-A72 + Quad Cortex-A53, 64-bit CPU

- Frequency is over 1.8GHz (Big cluster)

- L1 cache

- 48KB Icache and 32KB Dcache for each A72

- 32KB Icache and 32KB Dcache for each A53

- L2 cache

- 1024KB for big cluster

- 512KB for little cluster

- Internal SRAM

- 192KB total

- 4KB used by bootrom when bootup

- GPU:

- Mali-T864 GPU, OpenGL ES1.1/2.0/3.0/3.1, OpenCL, DX11

- Supports AFBC (ARM Frame Buffer Compression)

- Display:

- Dual VOP: one supports 4096x2160 with AFBC supported;The other supports 2560x1600

- Dual channel MIPI-DSI (4 lanes per channel)

- eDP 1.3 (4 lanes with 10.8Gbps) to support display, with PSR

- HDMI 2.0 for 4K 60Hz with HDCP 1.4/2.2

- DisplayPort 1.2 (4 lanes, up to 4K 60Hz)

- Supports Rec.2020 and conversion to Rec.709

- Camera:

- Dual mipi CSI,dual ISP,Maximum input resolution of 13M pixels

- Memory:

- Dual channels 64-bit DRAM controller

- Support DDR3/DDR3L, LPDDR3, LPDDR4

- Connectivity:

- PCIe 2.1 (4 full-duplex lanes with 20Gbps)

- Embedded low power MCU for other application

- 8 channels I2S supports 8 channels RX or 8 channels TX

Source: [2]

There is a "hidden" low-power, low-cost Cortex-M0 MCU. It implements power-management functionality and helpers (e.g. DRAM frequency switching support). [3]

External

- Rockchip Wiki on RK3399 [4]